DEC V-11

The V-11, code-named "Scorpio", is a miniprocessor chip set implementation of the VAX instruction set architecture (ISA) developed and fabricated by Digital Equipment Corporation (DEC).

History

[edit]The V-11 was Digital's first VAX microprocessor design, but was the second to ship, after the MicroVAX 78032. It was presented at the 39th International Solid State Circuits Conference held in 1984 alongside the MicroVAX 78032 and was introduced in early 1986 in systems, operating at 5 MHz (200 ns cycle time) and in 1987 at 6.25 MHz (160 ns cycle time). The V-11 was proprietary to DEC and was only used in their VAX 8200, VAX 8250, VAX 8300 and VAX 8350 minicomputers; and the VAXstation 8000 workstation.

At 5 MHz, the V-11 performed approximately the same as the VAX-11/780 superminicomputer. At 6.25 MHz, it performed approximately 1.2 times faster than the VAX-11/780.

The V-11 was part of the Scorpio program, which aimed at providing DEC with the ability to develop and fabricate very-large-scale integration (VLSI) integrated circuits (ICs). Other aspects of the program were the development of a new computer-aided design (CAD) suite and semiconductor process, the results of which are CHAS and ZMOS, respectively. ZMOS was the first semiconductor process to be developed entirely by DEC.

Description

[edit]The V-11 was a multichip design, mainly consisting of an I/E chip, a M chip, a F chip and five ROM/RAM chips. Unlike the MicroVAX 78032, which implemented a subset of VAX ISA, the V-11 was a complete VAX implementation, supporting all of the 304 instructions and 17 data types (byte, word, longword, quadword, octaword, F-floating, D-floating, G-floating, H-floating, bit, variable-length bit field, character string, trailing numeric string, leading separate numeric string, packed decimal string, absolute queue, and self-relative queue).

The chips in the chip set were connected with four buses: the MIB, DAL, PAL and CAL. The MIB (microinstruction bus) carried microinstructions control signals and addresses from the control store to the I/E and F chips. The MIB is 40 bits wide, the same width as a microword and is parity protected. The DAL is a 32-bit parity-protected bus that carries data and addresses to and from the I/E, M and F chips, cache, backup translation buffer RAMs and the port interface.

ROM/RAM chip

[edit]The ROM/RAM chip (DC327) implemented one-fifth of the patchable control store. It contained a 16,384 by 8-bit (16 KB) read-only memory (ROM), a 1,024 by 8-bit (1 KB) random-access memory RAM and a 32 by 14-bit content-addressable memory (CAM). The ROM contained the control store, with the RAM used to hold control store patches. The ROM/RAM consisted of 208,000 transistors on a die measuring 344 mils by 285 mils (8.74 mm by 7.24 mm) for an area of 98,040 mil2 (63.25 mm2). It dissipated 1 W.

Five DC327 chips were mounted on a common ceramic carrier in a very characteristic, overly wide DIP package. The package provided the complete control store as a unit for the processor; each of the five DC327 had different ROM contents.

I/E chip

[edit]

The I/E chip (DC328) contained an instruction buffer, a microsequencer, an execution unit and a mini-translation buffer (MTB). The instruction buffer is a two-entry 32-bit buffer that held prefetched instructions. It improved performance by maintaining a number of instructions ready for execution. The hardware attempted to keep the instruction buffer full at all times. The execution unit consisted of sixteen 32-bit general purpose registers defined by the VAX ISA, an arithmetic logic unit (ALU) and a shifter. The MTB is a translation lookaside buffer (TLB). It contained five page table entries (PTEs), one for instruction and four for data. In the event of a miss, the backup translation buffer (BTB) in the M chip is used. The I/E chip consisted of 60,000 transistors on a die measuring 354 mils by 358 mils (8.99 mm by 9.09 mm) for an area of 126,732 mil2 (81.76 mm2). It dissipated 5 W.

M chip

[edit]The M chip (DC329) was responsible for memory management and interrupt handling. It contained the backup translation buffer (BTB) tags, cache tags and internal processor registers. The M chip also contained the I/O functionality defined by the VAX architecture and generated the clock signal for the chip set.

The backup translation buffer was essentially a translation lookaside buffer (TLB) which handled a miss in the MTB. The BTB contained 512 page table entries (PTEs), of which 256 were for system-space pages and 256 were for process-space pages. There are 128 BTB tags, one for every four PTEs, located in the M chip. The BTB was implemented with external RAMs.

There are 26 internal processor registers, which are used by the microcode for temporary storage when executing complex instructions requiring multiple cycles.

The M chip consisted of 54,000 transistors on a die measuring 339 mil by 332 mil (8.61 mm by 8.43 mm) for an area of 112,548 mil2 (72.61 mm2). It dissipated 3 W.

F chip

[edit]The F chip (DC330) contained a floating-point unit (FPU). It supported most VAX floating-point instructions and the f_floating, d_floating and g_floating data types defined in the VAX architecture and was also responsible for executing integer divide and multiply instructions. The F chip received opcodes from the I/E chip and microinstructions from the control store over the MIB bus. Operands were received from the memory or the general purpose registers over the DAL bus, which is also used to write back results. It consisted of 29,600 transistors on a 341 mil by 288 mil die (8.66 mm by 7.32 mm) for an area of 98,208 mil2 (63.36 mm2). It dissipated 2.5 W.

The F chip was a derivative of the FPA, which belonged to the J-11 microprocessor chip set, an implementation of the PDP-11. The F chip was supposed to be a completely new design developed for the V-11, but was cancelled in favor of a derivative as part of an effort to simplify the V-11 so it could be completed quicker as development of the MicroVAX 78032 had begun.

Cache

[edit]The V-11 has an external 8 KB primary cache. The cache was physically addressed and has a 64-byte cache block.

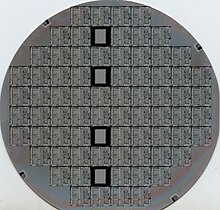

Physical

[edit]The V-11 chip set contained a total of 1,183,600 transistors spread over nine dies fabricated in Digital's ZMOS process, a 3.0 μm NMOS process with two levels of interconnect. (The 'Z' in the name was chosen because it looked like a '2' -- having 2 layers of metal was notable.)

References

[edit]- "KA820/KA825 Processor Technical Manual, Third Edition, April 1987". EK-KA820-TM-003. Digital Equipment Corporation.

Further reading

[edit]- Johnson, W.N.; Herrick, W.V.; Grundmann, W.J. (October 1984). "A VLSI VAX chip set". IEEE Journal of Solid-State Circuits 19 (5): 663–674.

- Johnson, W. (February 1984). "A VLSI superminicomputer CPU". ISSCC Digest of Technical Papers: 174–175.